近日,清华大学微纳电子系、北京未来芯片技术高精尖创新中心副教授高滨联合多家合作单位,在《自然·电子》(Nature Electronics)在线发表了题为“类脑计算芯片”(Neuro-inspired computing chips)的综述文章。该文章系统介绍了类脑计算芯片的历史、现状与未来展望,并重点分析了存算一体芯片的设计方法与研究挑战。

芯片算力是人工智能(AI)技术的三大要素之一。传统计算芯片是基于场效应晶体管、数字逻辑运算和冯诺依曼架构设计的,其优势在于高精度的数据处理。近年来,AI应用对数据计算量的需求呈爆炸式增长,与传统计算芯片算力的渐趋饱和形成了尖锐的矛盾,严重制约了AI技术的进一步发展。新型的存算一体芯片通过模拟生物大脑的结构和信息处理机制,可以显著的提升AI任务的计算效率,弥补传统计算芯片的不足,在终端智能电子设备和云端服务器等领域都有着巨大的发展潜力和应用前景。

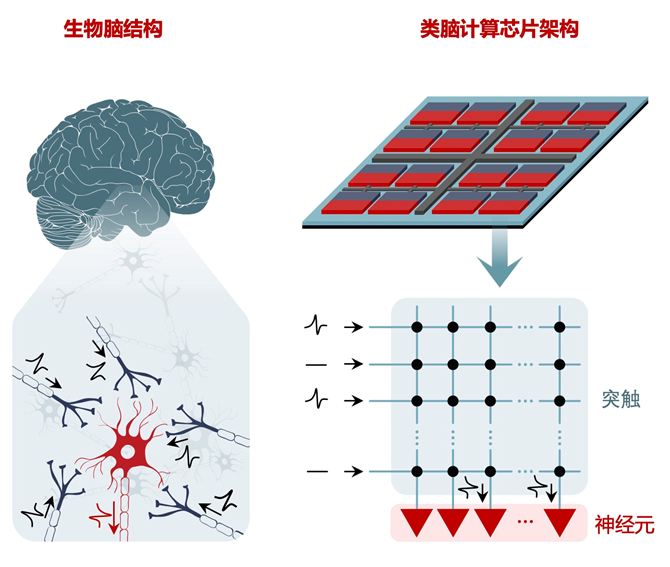

生物大脑与存算一体芯片

存算一体是大脑最主要的特征之一,也是实现高算力、高能效计算的一项关键技术。由于存算一体芯片利用存储器件的模拟特性进行计算,电路中的各类误差给芯片设计带来了巨大的挑战。只有通过从器件到电路再到架构和算法的协同优化,才可能使存算一体芯片的计算精度得到保持,并同时获得算力和能效的大幅提升。本篇综述对存算一体器件的特性、可靠性与良率需求、存算一体阵列结构选择、存算一体电路设计方法、架构优化方法、算法编译与映射方法、片上训练方法等都做了详细分析,总结出了协同设计技术及设计自动化(EDA)工具链的整体框架,并对存算一体芯片的未来发展趋势作了展望。

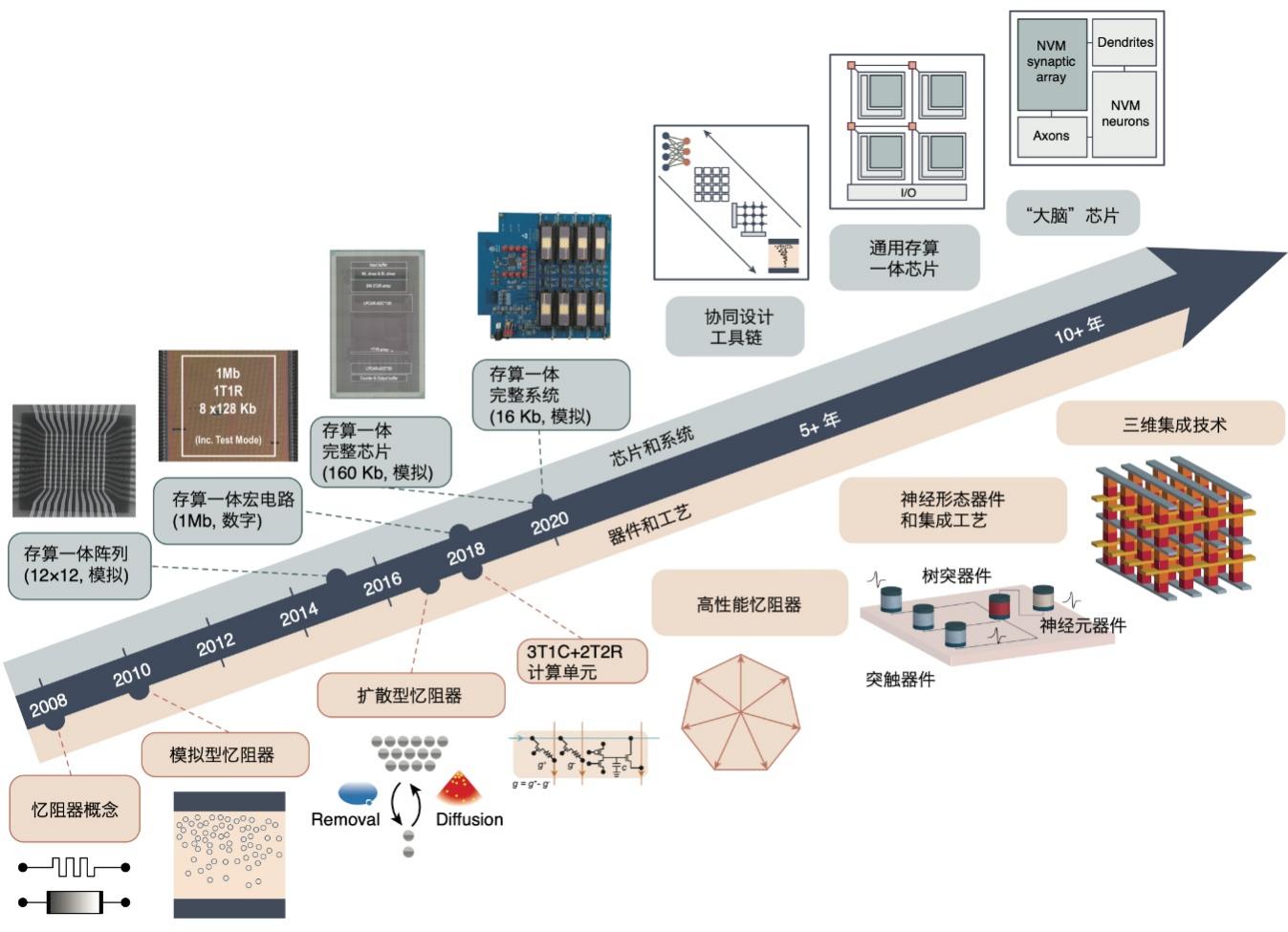

存算一体芯片发展路线图

器件方面:以忆阻器为代表的神经形态器件在不断优化中,未来将继续提升性能并发展大规模集成技术,实现多种神经形态器件的异质集成和三维高密度集成。

芯片方面:小规模的存算一体宏电路在持续完善,未来将打通协同设计技术链条,研制出规模可扩展的通用型存算一体芯片和基于多种神经形态器件的类脑计算芯片。

高滨副教授一直从事忆阻器性能优化和存算一体芯片设计方法的相关研究,成功开发了从器件到系统的联合仿真工具和协同优化方法,设计出计算精度大于95%、能效大于78TOPs/W的高性能忆阻器存算一体芯片,相关成果在国际电子器件会议(IEDM)、超大规模集成电路会议(VLSI)、国际固态电路会议(ISSCC)、设计自动化会议(DAC)等顶级会议上发表。除了受邀撰写本篇综述以外,高滨还于2019年在《自然·通讯》(Nature Communications)上发表了关于忆阻器机理与模型的综述,2020年在《国际电机电子工程师学会汇刊》(Proceedings of the IEEE)上发表了关于存算一体器件与电路的综述。

清华大学微纳电子系钱鹤教授、吴华强教授团队围绕存算一体芯片开展了系统的研究,近两年在《自然》(Nature)、《自然·纳米科技》(Nature Nanotechnology)、《自然·通讯》(Nature Communications)等期刊发表了多篇文章。本篇综述的通讯作者是吴华强教授,共同第一作者是高滨和博士生章文强,共同作者还包括台湾新竹清华大学张孟凡教授、韩国科学技术院柳会俊(Hoi-Jun Yoo)教授以及清华大学微纳电子系的姚鹏博士、唐建石助理教授和钱鹤教授等。

论文链接:https://www.nature.com/articles/s41928-020-0435-7

来源:清华新闻网

010-62772847

010-62772847 kyyyb@tsinghua.edu.cn

kyyyb@tsinghua.edu.cn 版权所有 © 清华大学科研院

版权所有 © 清华大学科研院 总浏览人数:

总浏览人数:

010-62772847

010-62772847 kyyyb@tsinghua.edu.cn

kyyyb@tsinghua.edu.cn 版权所有 © 清华大学科研院

版权所有 © 清华大学科研院 总浏览人数:

总浏览人数: